Based on slides by Harsha V. Madhyastha

### EECS 482 Introduction to Operating Systems Spring/Summer 2020 Lecture 12: Multilevel paging and eviction

Nicole Hamilton https://web.eecs.umich.edu/~nham/ nham@umich.edu

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

### Midterm exam

Online using *Crabster.org* Wed Jun 24 3:00 to 5:00 pm EDT.

If you need an accommodation, please let us know soon. Material for midterm:

- 1. All the lecture topics from start until end of lecture 9 on deadlock.

- 2. All the labs on these topics.

- 3. Projects 1 and 2.

### Midterm exam

Two sample exams posted on web page.

Solutions in lab section this Friday.

Review session Sat Jun 20 12:00 noon to 3:00 pm EDT.

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

### **Dynamic address translation**

Break the requirement that the process space be contiguous.

MMU strategies we'll discuss:

- 1. Base and bounds.

- 2. Segmentation.

- 3. Paging.

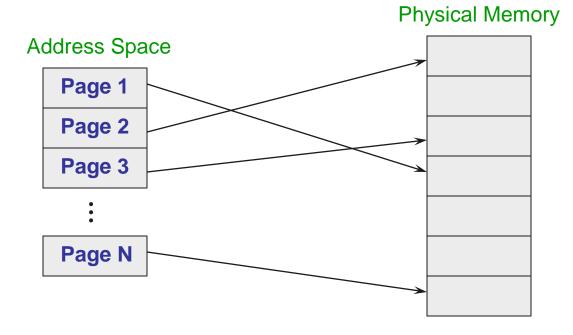

### Allocate phys. memory in fixed-size units (pages) Any free physical page can store any virtual page

8

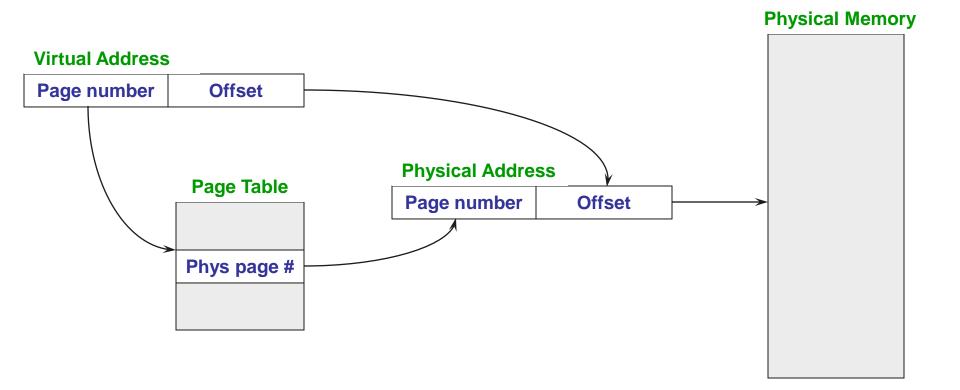

# Page Lookups

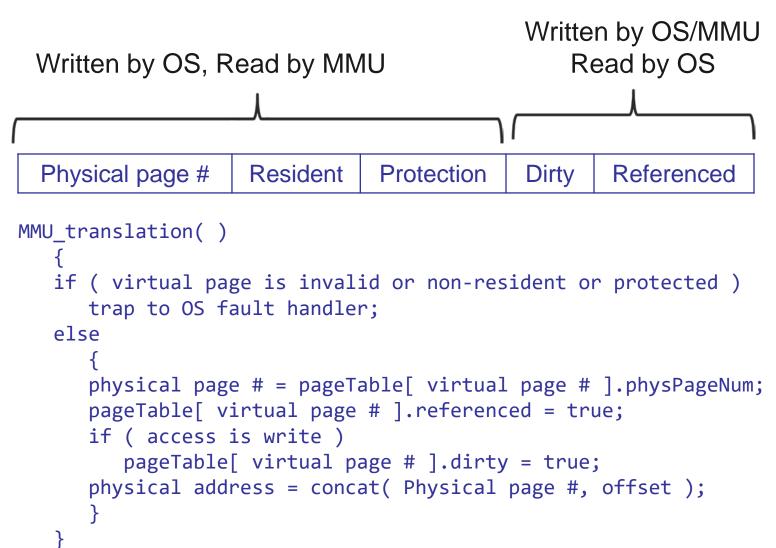

Each virtual page can be in physical memory or "paged out" to disk.

Pages can also have different protections (e.g., read, write, execute).

```

MMU_translation( )

{

if ( virtual page is

invalid or non-resident or protected )

trap to OS fault handler;

else

{

physical page # =

pageTable[ virtual page # ].physPageNum;

physical address =

concat( Physical page #, offset );

}

}

}

```

| Virtual page # | Physical page # | Resident | Protection |

|----------------|-----------------|----------|------------|

| 0              | 105             | 0        | RX         |

| 1              | 15              | 1        | R          |

| 2              | 283             | 1        | RW         |

| 3              | invalid         |          |            |

|                | invalid         |          |            |

| 1048575        | invalid         |          |            |

Valid  $\rightarrow$  virtual page is legal for process to access.

Resident  $\rightarrow$  virtual page is valid and in physical memory.

Error to access invalid page, but not to access non-resident page.

| Virtual page # | Physical page # | Resident | Protection |

|----------------|-----------------|----------|------------|

| 0              | 105             | 0        | RX         |

| 1              | 15              | 1        | R          |

| 2              | 283             | 1        | RW         |

| 3              | invalid         |          |            |

|                | invalid         |          |            |

| 1048575        | invalid         |          |            |

Causes of a page fault:

- 1. Invalid page or disallowed by protection bits, often a user bug.

- 2. Not resident and must be brought in by the OS.

### Page table size

Page size is typically 4 KB or 8 KB.

Some architectures support multiple page sizes.

*Each process* with a 32-bit address space with 4-byte page table entries requires:

$$\left(\frac{2^{32}}{4096}\right) * 4 = 4 MB$$

A 64-bit address space with 8-byte entries requires:

$$\left(\frac{2^{64}}{4096}\right) * 8 = 3.6 * 10^{16} = 36 \, PB$$

#### Pros

- 1. Simple memory allocation.

- 2. Flexible sharing.

- 3. Easy to grow address space.

#### Cons

1. Large page table size.

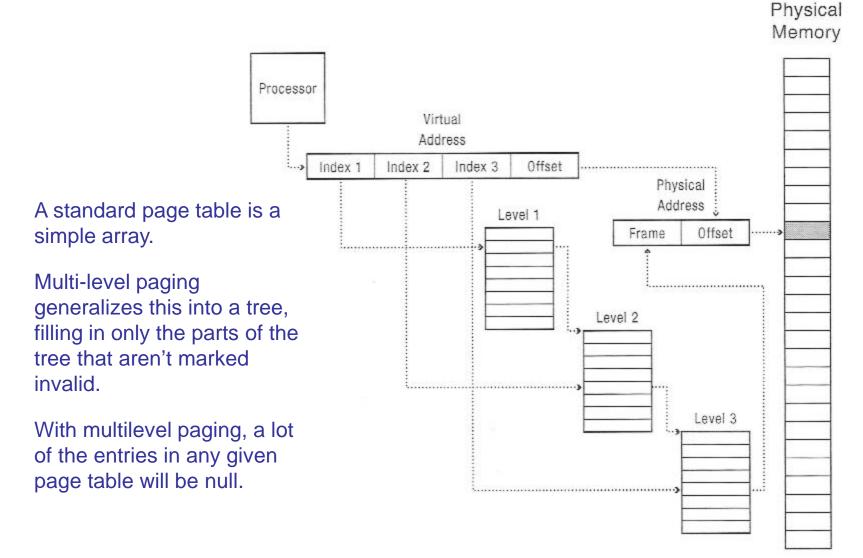

But the vast majority of all page table entries will be marked invalid.

### **Sparse Address Space**

Most processes use only a tiny fraction of their 32 or 64-bit address space.

They usually have a huge hole in the middle.

So we only need to represent that part of the page table that isn't marked invalid.

| Stack   |

|---------|

| Invalid |

| Неар    |

| Code    |

| Virtual<br>page # | Physical page # |

|-------------------|-----------------|

| 0                 | 105             |

| 1                 | 15              |

| 2                 | 283             |

| 3                 | invalid         |

|                   | invalid         |

| 1048572           | invalid         |

| 1048573           | 1078            |

| 1048574           | 48136           |

| 1048575           | 60              |

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

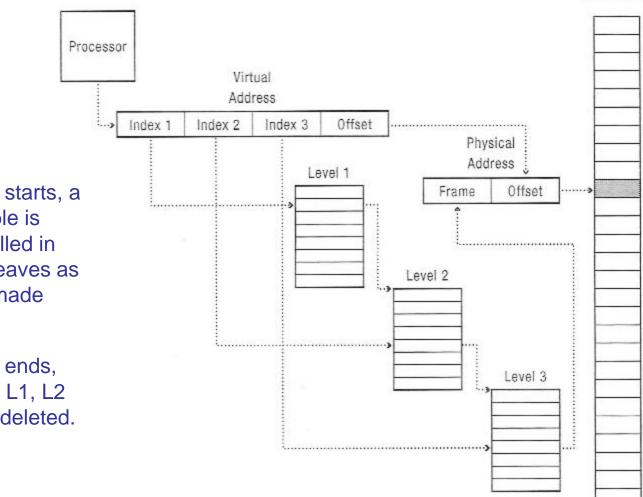

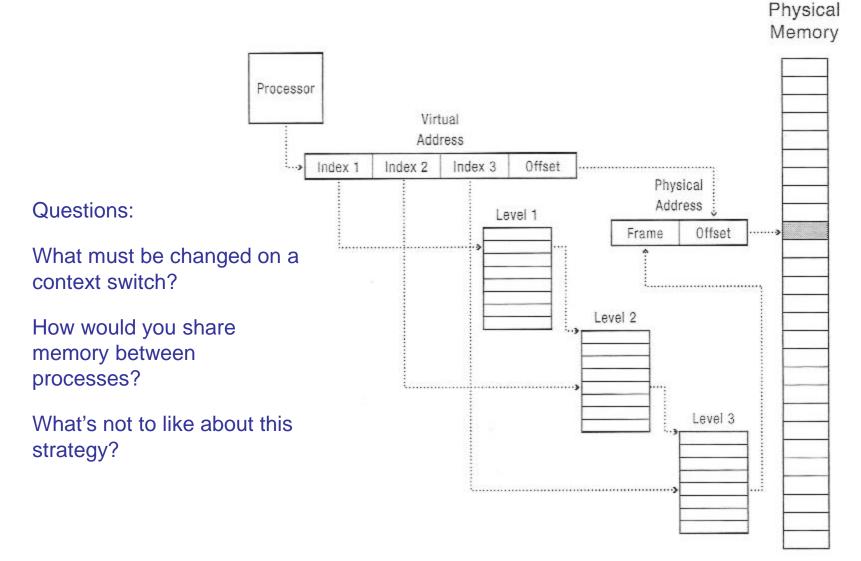

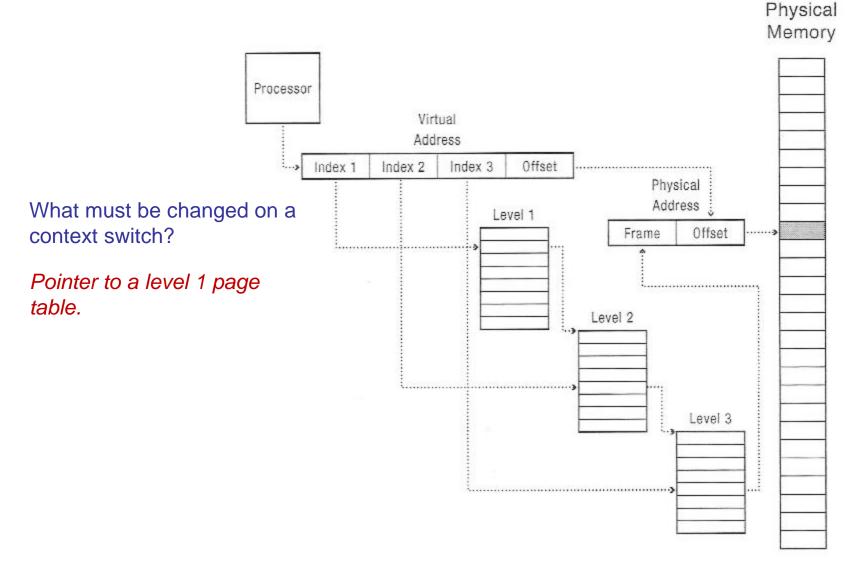

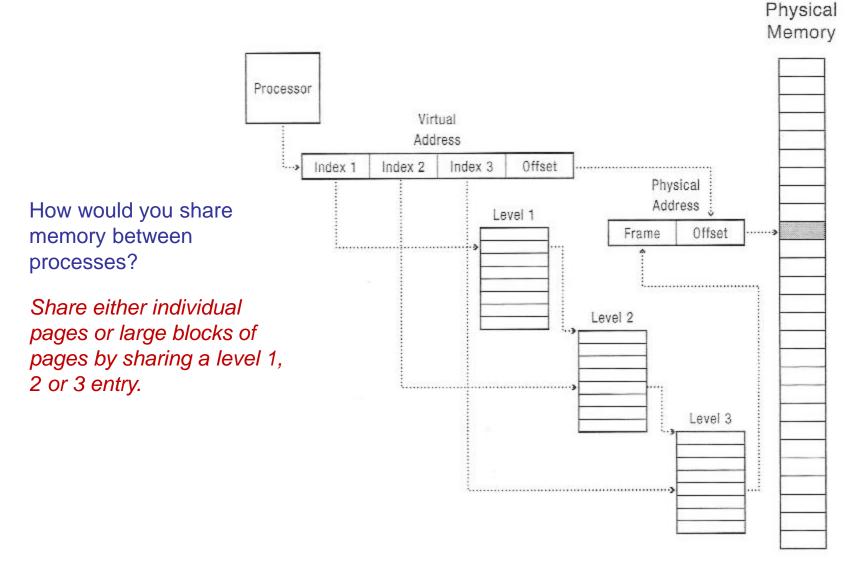

Physical Memory

When a process starts, a new L1 page table is allocated, then filled in with L2 and L3 leaves as new pages are made valid.

When a process ends, the entire tree of L1, L2 and L3 tables is deleted.

#### Pros

- 1. Simple memory allocation.

- 2. Flexible sharing.

- 3. Easy to grow address space.

- 4. Space-efficient representation of the page table.

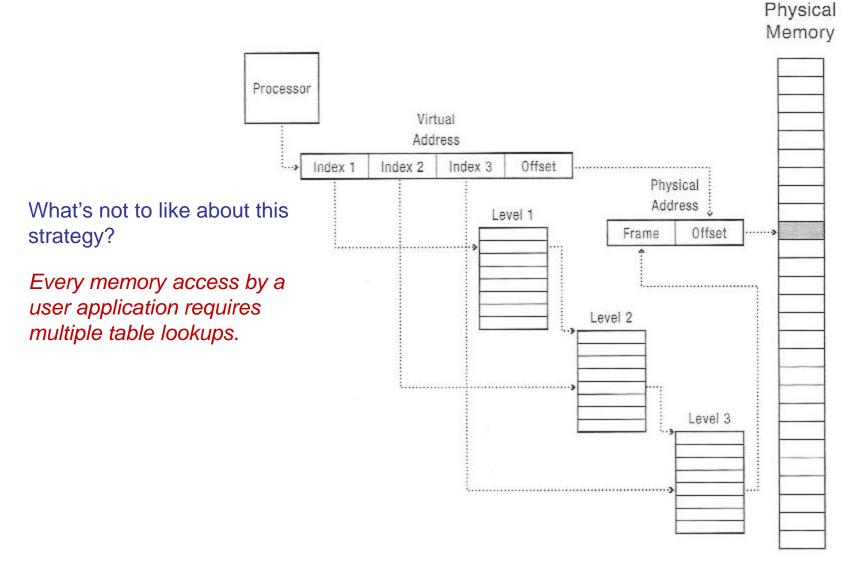

#### Cons

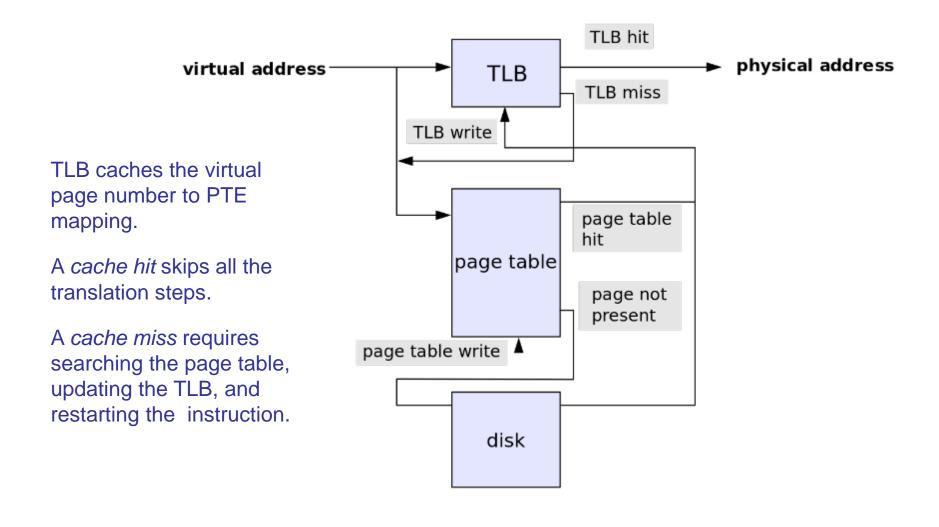

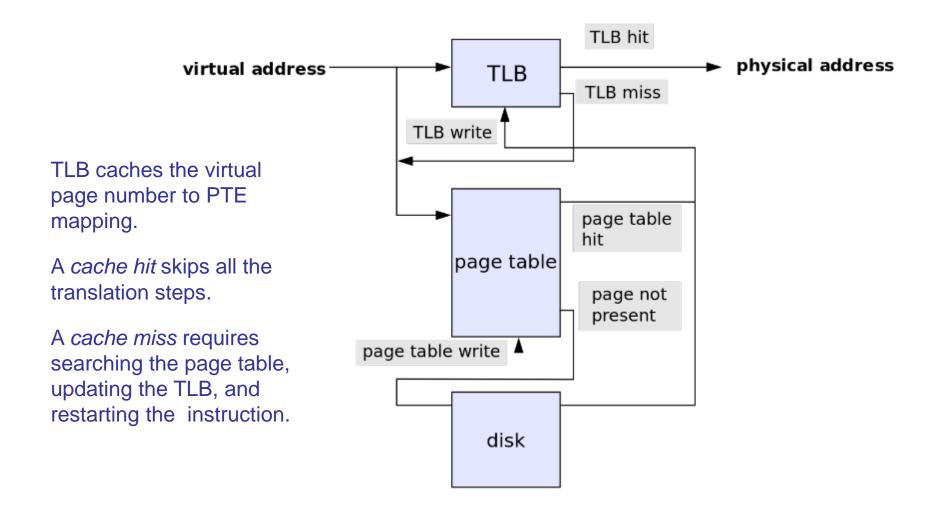

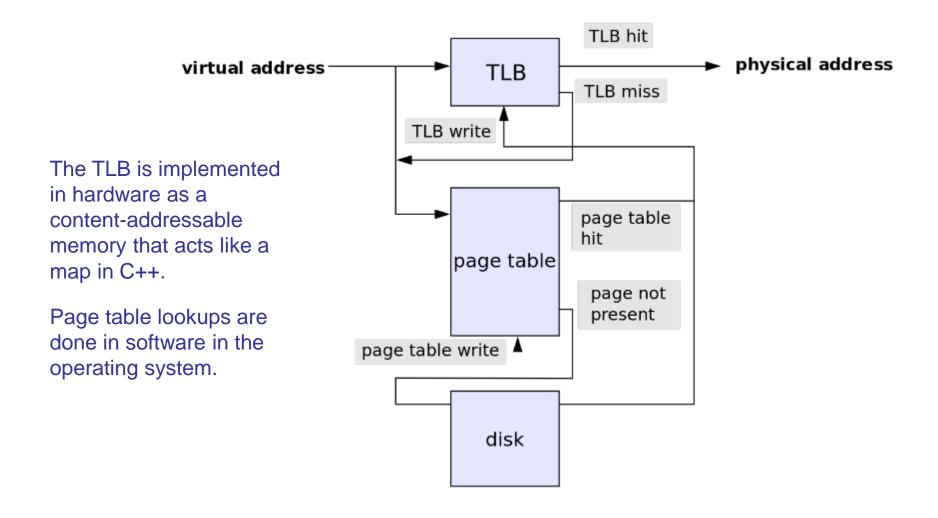

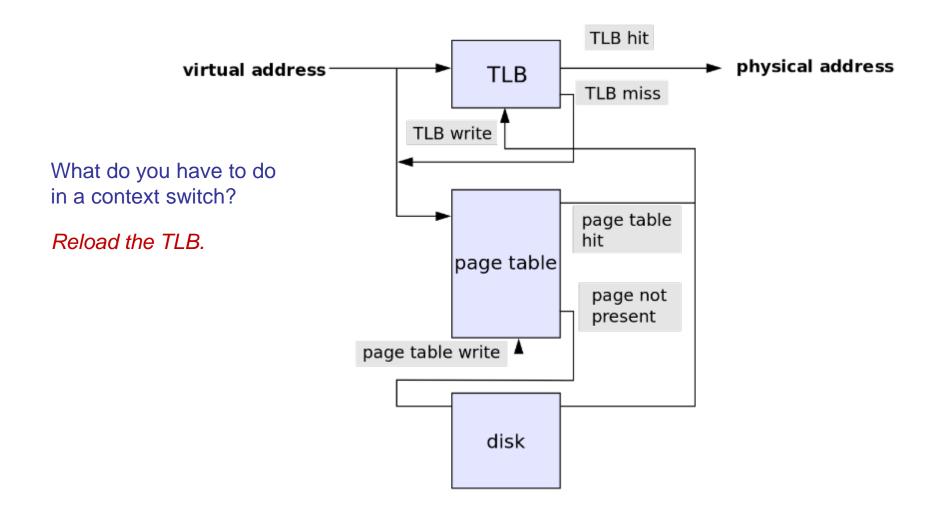

1. Two or more extra lookups per memory reference.

What could be done to solve this? We can cache the translations in hardware.

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

### Page replacement

Not at all valid pages can be in physical memory.

Must decide how to handle loads/stores to non-resident pages.

Sometimes, we will need to *evict* a page to make room for another.

# Agenda

- 1. Midterm.

- 2. Paging.

- 3. Multilevel paging.

- 4. Translation lookaside buffer.

- 5. Eviction.

### Page Replacement

Not all valid pages may fit in physical memory

Some pages must be paged out (written) to disk.

Disk is the "backing store", physical mem acts as cache.

To read in a page from disk, some resident page may need to be paged out, *"evicted",* first.

Need an algorithm to decide which page to evict to make space. Goal: minimize page faults.

# **Replacement policies**

Possibilities:

- 1. Random.

- 2. First in, first out (FIFO).

- 3. An imaginary optimum.

- 4. Least recently used (LRU).

### FIFO

Under FIFO, we replace the oldest page brought into memory. May replace pages that continue to be frequently used.

| Α | В | С | D | С | Е | Α | С | D | В | С |

|---|---|---|---|---|---|---|---|---|---|---|

| Α | А | А | А | А | Е | Е | Е | Е | Е | Е |

|   | В | В | В | В | В | А | А | А | А | А |

|   |   | С | С | С | С | С | С | С | В | В |

|   |   |   | D | D | D | D | D | D | D | С |

Header row is sequence of accesses to 5 virtual pages A thru E that are paged in and out of 4 physical pages in memory, represented by the rows.

Each cell indicates what virtual page is in that physical page.

### Optimal replacement

Under an optimal strategy, we would replace the page that won't be used again for the longest time, minimizing cache misses.

But that requires knowledge of the future!

| Α | В | С | D | С | Е | Α | С | D | В | С |

|---|---|---|---|---|---|---|---|---|---|---|

| Α | А | А | А | А | А | А | А | А | А | А |

|   | В | В | В | В | Е | Е | Е | Е | В | В |

|   |   | С | С | С | С | С | С | С | С | С |

|   |   |   | D | D | D | D | D | D | D | D |

Header row is sequence of accesses to 5 virtual pages A thru E that are paged in and out of 4 physical pages in memory, represented by the rows.

Each cell indicates what virtual page is in that physical page.

### LRU

Under LRU, we approximate the optimal solution by using past references. If a page hasn't been used for a while, we assume it probably won't be used again anytime soon.

| Α | В | С | D | С | Е | Α | С | D | В | С |

|---|---|---|---|---|---|---|---|---|---|---|

| Α | А | А | А | А | А | А | А | А | А | А |

|   | В | В | В | В | Е | Е | Е | Е | В | В |

|   |   | С | С | С | С | С | С | С | С | С |

|   |   |   | D | D | D | D | D | D | D | D |

Header row is sequence of accesses to 5 virtual pages A thru E that are paged in and out of 4 physical pages in memory, represented by the rows.

Each cell indicates what virtual page is in that physical page.

Why would this work well?

### LRU

Works well because of temporal locality: Recently accessed pages are often accessed again. Surprisingly good approximation of the optimum and hard to beat.

| Α | В | С | D | С | Е | Α | С | D | В | С |

|---|---|---|---|---|---|---|---|---|---|---|

| A | А | А | А | А | А | А | А | А | А | А |

|   | В | В | В | В | Е | Е | Е | Е | В | В |

|   |   | С | С | С | С | С | С | С | С | С |

|   |   |   | D | D | D | D | D | D | D | D |

Header row is sequence of accesses to 5 virtual pages A thru E that are paged in and out of 4 physical pages in memory, represented by the rows.

Each cell indicates what virtual page is in that physical page.

But could there be situations where doesn't work?

### LRU

But depending on the access pattern, it can sometimes it can be very wrong!

| Α | В | С | D | Е | Α | В | С | D | Е | Α |

|---|---|---|---|---|---|---|---|---|---|---|

| Α | А | А | А | Е | Е | Е | Е | D | D | D |

|   | В | В | В | В | Α | А | А | А | Е | Е |

|   |   | С | С | С | С | В | В | В | В | Α |

|   |   |   | D | D | D | D | С | С | С | С |

Header row is sequence of accesses to 5 virtual pages A thru E that are paged in and out of 4 physical pages in memory, represented by the rows.

Each cell indicates what virtual page is in that physical page.

# Approximating LRU

Can't afford to timestamp every access and maintain an actual queue, so we approximate with hardware support.

Most MMUs maintain a "referenced" bit for each resident page. Set by MMU when page is read or written. Can be cleared by OS.

How to use reference bit to identify old pages?

Clear reference bit for all pages. After some time, examine reference bits. Reference bit = 0 for pages not accessed recently.

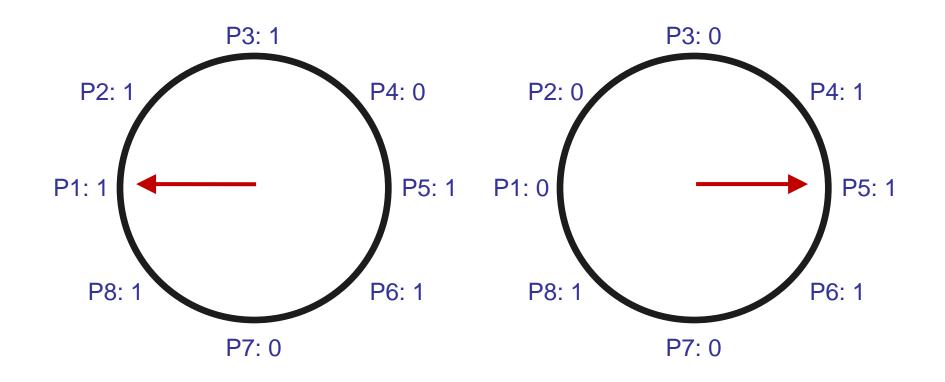

# Clock replacement algorithm

Arrange resident pages around a clock.

(You'll do this in project 3.)

To select a page for eviction:

- 1. Consider page pointed to by clock hand.

- 2. If not referenced, evict page.

- 3. If referenced, clear reference bit.

- 4. Continue until a page is found that hasn't been referenced.

### **Clock example**

What if all pages referenced since last sweep?

### Page eviction

Some questions.

1. Where does the evicted page go?

It will go to disk.

2. When do you not need to write page to disk?

When it's not been changed. Rely on hardware to maintain dirty bit in PTE.

3. Why not write to disk on every store?

Would make every write as slow as the disk. Write to disk only when necessary.

4. How can you optimize eviction?

Why no valid bit in PTE?

All invalid virtual pages are non-resident.

Valid non-resident pages: where's the disk block?

OS must maintain this, MMU simply traps to OS.

How can we make do without resident bit?

Clear protection bits when non-resident to cause hardware fault.

#### Can we make do without the dirty bit?

Have OS set the dirty bit itself.

Naive solution: Trap on every store & mark dirty.

How to reduce # of page faults?

Only care about transition from clean to dirty. Clean pages have 0 write protection bit. Dirty pages have usual value.

#### Can we make do without the dirty bit?

Have OS set the dirty bit itself.

Naive solution: Trap on every store & mark dirty.

How to reduce # of page faults?

Only care about transition from clean to dirty. Clean pages have 0 write protection bit. Dirty pages have usual value.

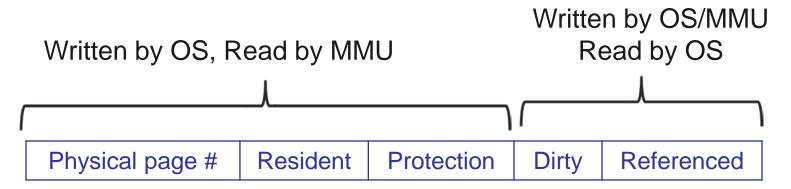

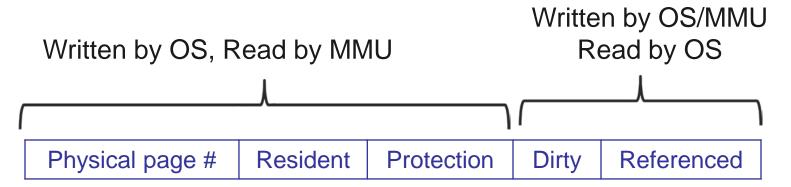

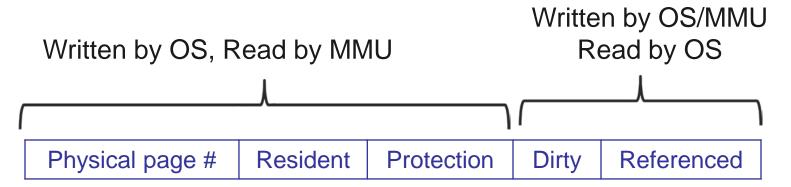

### Page table contents

Physical page # Protection Referenced

Can we make do without referenced bit?

Can use similar trick as that used for dirty bit Insight: only care about unreferenced  $\rightarrow$  referenced

MMU simpler but page fault handler more complex